Replay2

Well, here we are at the end of 2024. Already.

I get a lot of questions along the lines of “where are we at”, “why is it taking so long” etc etc…

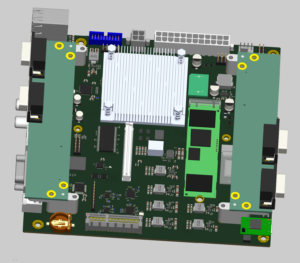

Replay2 is a complex board both electrically and mechanically. I am trying to do it at a low cost, which means a low layer count PCB. The design drawing (schematic) is complete and has been for a few months. I have most of the parts already to build the 10 initial prototypes.

The process of getting all the parts positioned on the board is pretty much done, and I’ve nearly finished routing it.

We had very early access and the tool support has come a long way since I first pinned the board out. Running the completed design through the tool showed a few problems but these are pretty much fixed. I’m really hoping to finish the PCB finally in the next few days and get the prototype boards back in January. This will still give us 2 months to check everything over before we start building boards in volume in the spring.

There are near daily updates on the discord, this link will work for 7 days.

https://discord.gg/Snp4Kq4X

Wishing everybody a fantastic New Year.

Cheers,

MikeJ

Replay2 design nearing completion

I’m not doing very well at posting updates here, the Discord is where to be to get the latest gossip as we struggle to complete the design. The link below will work for a week, I’ll post another update after that.

https://discord.gg/UFH<REMOVE>PxsMc

We are out of NDA with Intel now and the Agilex5 info is publicaly available – as is the tool support. Anybody can get a license, zero cost. We have 10 chips for the prototypes waiting for the PCB now.

I’ll be honest, I had expected to get the board out to manufacture last month so we are running late – but it’s a very complex design and we are trying to keep costs down as much as possible, which makes the design phase and PCB layout harder.

Replay2 is a Mini-ITX board with a state-of-the-art Intel 7nm Agilex 5 FPGA. It’s very fast and low power. We have high speed DDR4 memory for the CPUs (64 bit A76s running at 1.4GHz). We have new IoT Hyperram running at 200MHz which offers low latency access for cores. We also have an SDRAM compatible with MiSTer FPGA cores – so porting is dead easy.

There are two versions – names to be decided, but let’s call them R2Phat and R2Lite for now. R2Phat has an FPGA roughly four times the size of the DE10-Nano used for MiSTer. Lite’s FPGA is more modest, but still somewhat larger than that Cyclone V. There is a multimode digital video out which can do at least 4K@60. There is a high quality 30bit analog VGA output and high quality audio codec with digital out. Both boards also have a removable eMMC module for mass storage.

R2Phat has a 2-lane PCIe M.2 slot for SSD, along with an optional compute module expansion slot which has 4x PCIe Gen 3, MIPI display interfaces, Ethernet and miscellaneous I/O. Originally this was going to be an RK3588 module, but we are also looking at a CM5.

Both boards have an M.2 slot for SDIO WI-FI/BT module and dual (front/back) swappable I/O modules for things like DB9 or SNAC controller inputs. There are lots of USB2 and Phat has a multi-mode USB-C connector.

Hopefully I can show you the final board in June.

/MikeJ

Replay2 update

It’s been an exciting two months learning about the new Intel Agilex5 and the RK3588 used in our new Replay2 platform. The design and schematic are nearly completed – after a number of last minute changes/improvements.

Samples of the part are on the way and we’ll post some detailed layout images and specs of the board in the near future.

I’m also setting up a new X account, and then this website will get updated and new forums added.

The Agilex5 is a bleeding edge new FPGA which is faster and larger than any other competing Retro gaming system. The part we are using has dual 64 bit A55 and dual 64bit A75 processors on board. It’s the natural successor to the CycloneV device used on the MISTer DE10-nano board.

https://www.intel.com/content/www/us/en/products/details/fpga/agilex/5.html

Replay2 will be open source, we’ve started to move the repositories onto github. There is a lot of work to do, and it’s hugely delayed, but I think it’s been worth all the changes and it’s going to be an incredible platform.

/MikeJ