Gyruss Konami 503 Replacement

Took a quick break from the new Replay build system today and tested a batch of replacement 503 ICs.

They appear to work well, so I can ship the board back to it’s owner and get some desk space back!

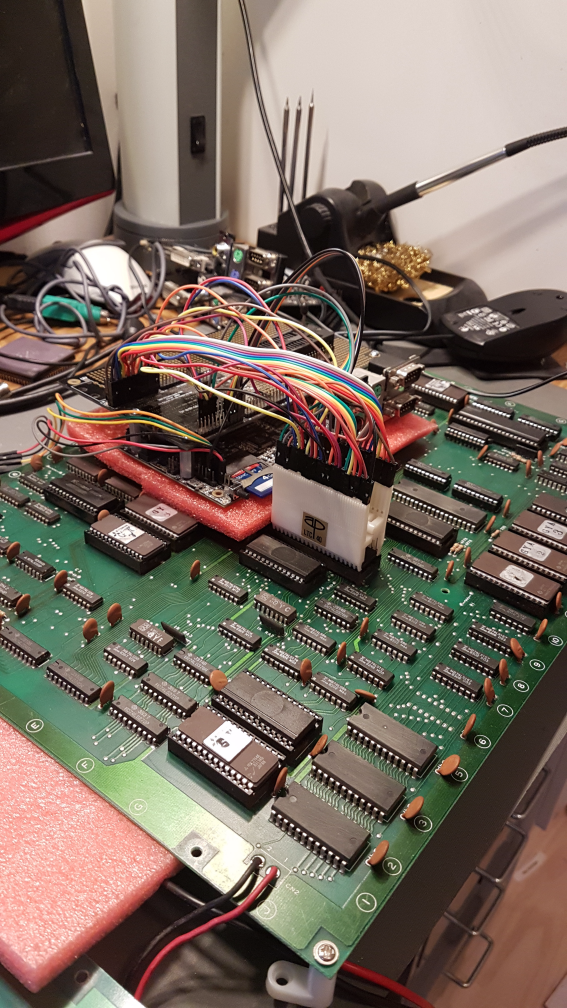

You can see the new 40 pin module working on the board below. I’ve got some left in stock, contact me if you need any – as well as a wide selection of 28 pin replacements.

/Mike

Konami 40 pin IC replacement

Finally, after being stuck in Swedish customs for nearly a month (thanks PostNord), the PCB for my 40 pin Konami 503 ASIC replacement has arrived.

I’m experimenting with an Atmel 5V CPLD on these, rather than the old Altera MAX7064 which is getting hard to get, and rather expensive. The PCB is double sided with a nearly solid ground plane on the bottom for good signal integrity and power stability.

Assuming these new parts function as expected the completed modules should work out around 24Euros each.

I appear to have got a bit carried away when ordering these boards, so if you want any let me know!

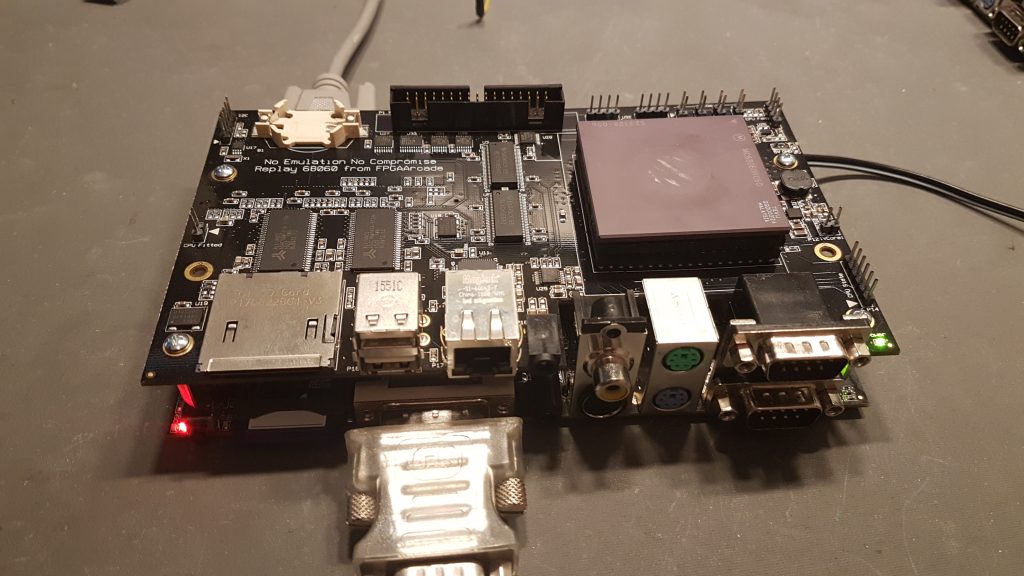

Last Replay1 shipped….

Well, actually the last (I thought) Replay1 shipped years ago, but I’ve had one sitting around which failed production test. When a core boots up, the ini file for that core tells the software which files to upload into the FPGA, and optionally these can be read back to verify everything is working correctly.

The system uses the same mechanism at start-up to check the DDR memory is behaving itself. This particular board was unique in failing this test.

2.827: [config.c:2095] tDirScan allocated: 7936 bytes

2.929: [fpga.c:363] FPGA:DRAM enabled, running test.

WARN: !!Match fail Addr: 0

2.932: [messaging.c:270] DumpBuffer: address = 0020ea78 ; size = 128 (0x80) bytes

2.940: [messaging.c:316] 0x00000000: 0004FFFF FFFF0004 FFFF0004 0004FFFF

3.000: [fpga.c:393] Should be:

3.009: [messaging.c:270] DumpBuffer: address = 0012d2c4 ; size = 128 (0x80) bytes

3.011: [messaging.c:316] 0x00000000: 0000FFFF FFFF0000 FFFF0000 0000FFFF

I had already replaced the DRAM chip and it hadn’t fixed the problem. An old tip is to press down hard on the BGA – and suddenly it was all good. With little to lose (apart from maybe setting fire to my office) I gave it a good roasting with the hot air gun. 300C for a few minutes seems to have done the trick.

It’s been on soak test all day and seems ok, so now I’ve cleared my desk it’s time to bring Replay2 into the world.

/MikeJ

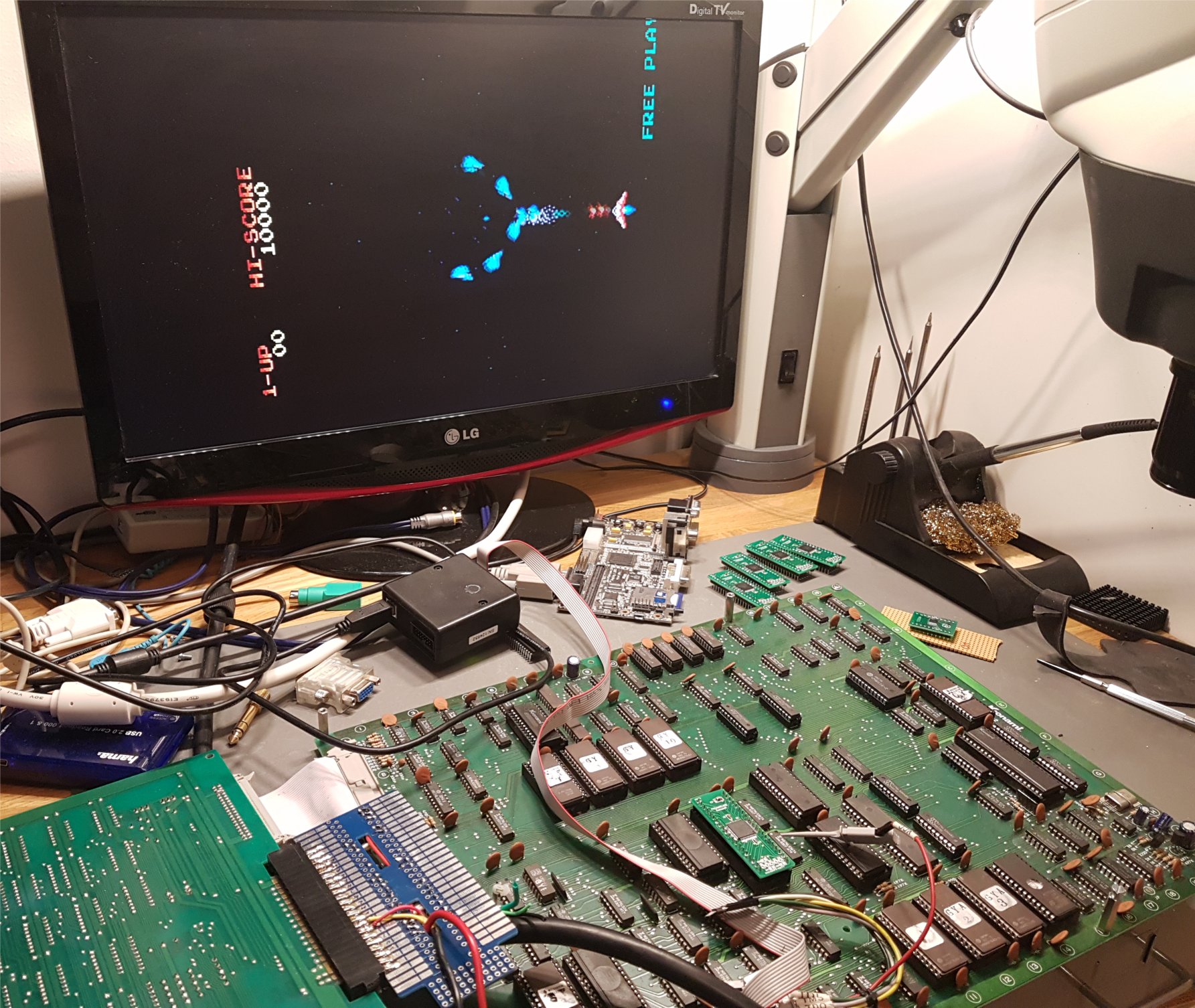

Gyruss reverse engineering

Here at FPGAArcade we’ve always tried to reproduce retro hardware for preservation as accurately as possible. When I did the first Pacman design years ago it was quite easy as there were only a few custom ICs. I built some analysis hardware you can find way back in the news here to compare the ASIC with my CPLD clone on the board in real time.

We have an extensive library of accurate replacements for the custom ICs on many boards. I produce CPLD modules which can be used to fix real arcade games – they are that accurate. This library is migrating to public github along with the rest of my designs asap.

I was lucky enough to be able to borrow a Gyruss game a few months ago and test the code. I decided to manufacture a 40 pin CPLD module to repair the board as well – although I’ve been waiting for it to clear customs here in Sweden for 3 weeks now 🙁

In the picture below, I’m using a Replay1 board with it’s debug daughterboard. This proves 5V isolation. Inside the FPGA I’m running the replacement design and a logic analyser core which compares all the IO in real time against the target board. Once the design is well understood, I can replace the custom ASIC with my CPLD board running the same code and see if it still works. Then we can produce an FPGA version of the complete game.