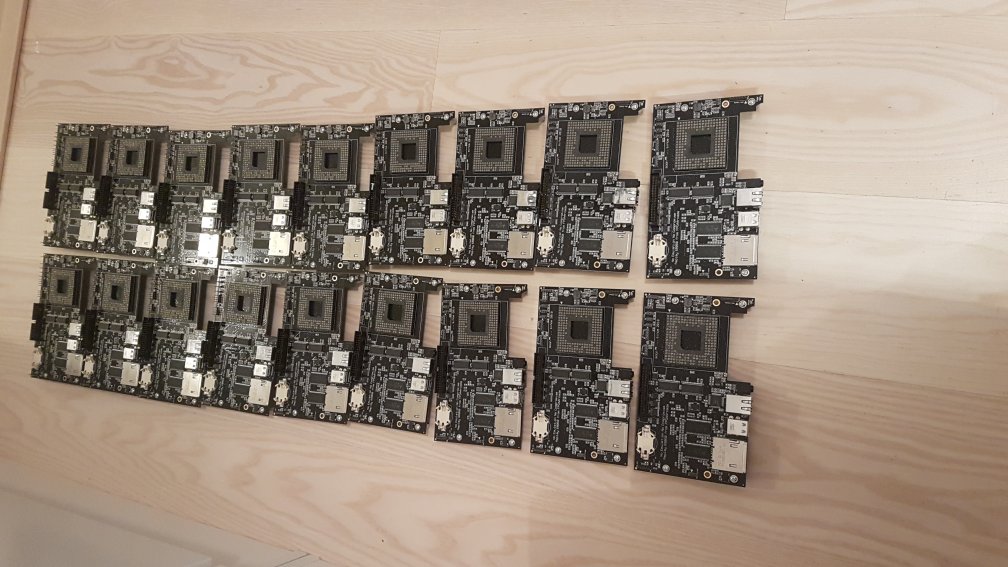

Replay2 proto-board arrived

We’ve bought a number of Ultra96 boards which contain a similar FPGA to the target device on Replay2. This will kick start development, especially on the Linux side. I’m also designing a small add-on board with the video output devices we’ll use on the real board. This will allow us to run up some cores and make sure we are happy with the architecture, as well as letting me crack on with testing the new 68K core in the Amiga.

Replay2 first mock up

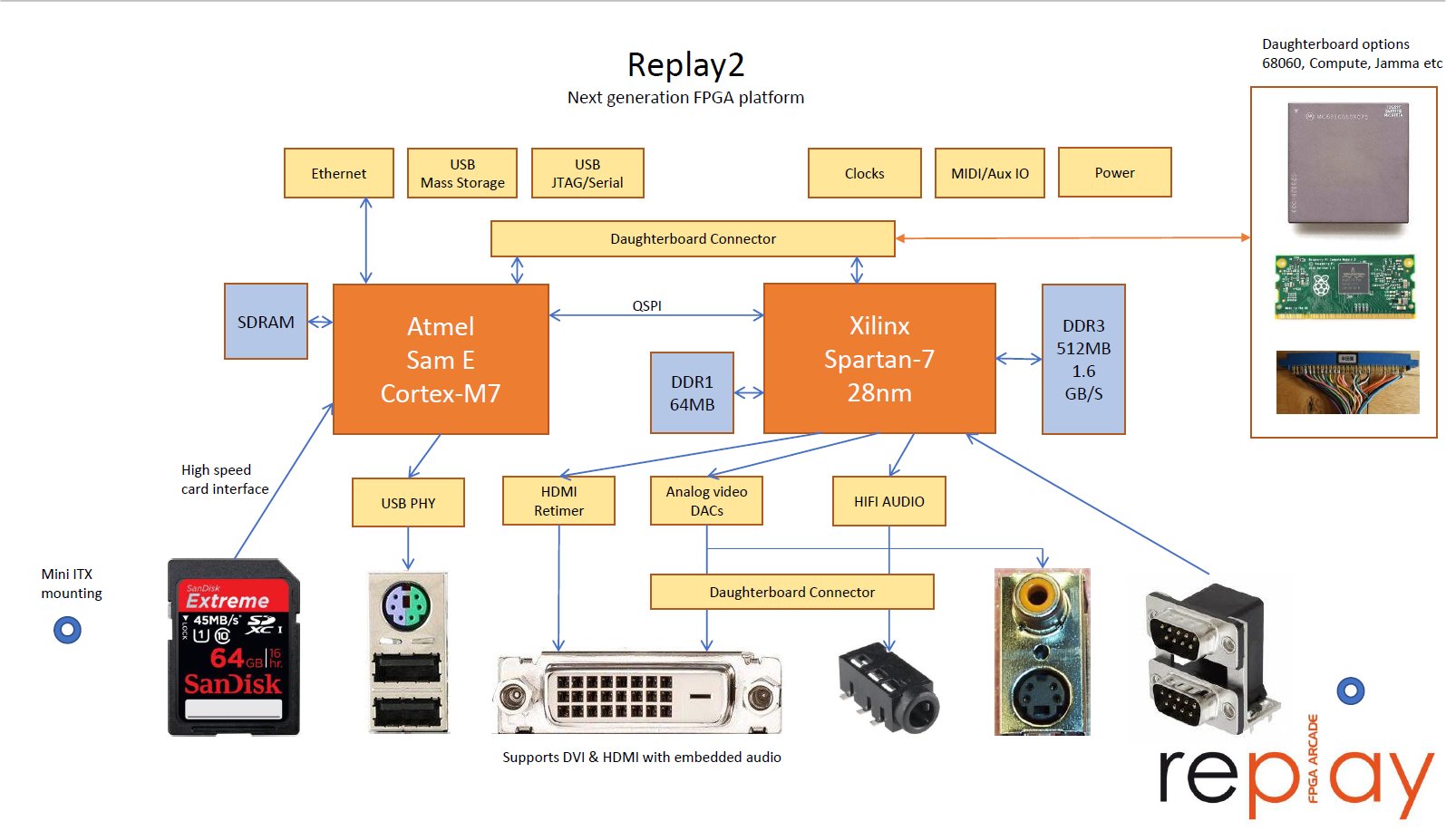

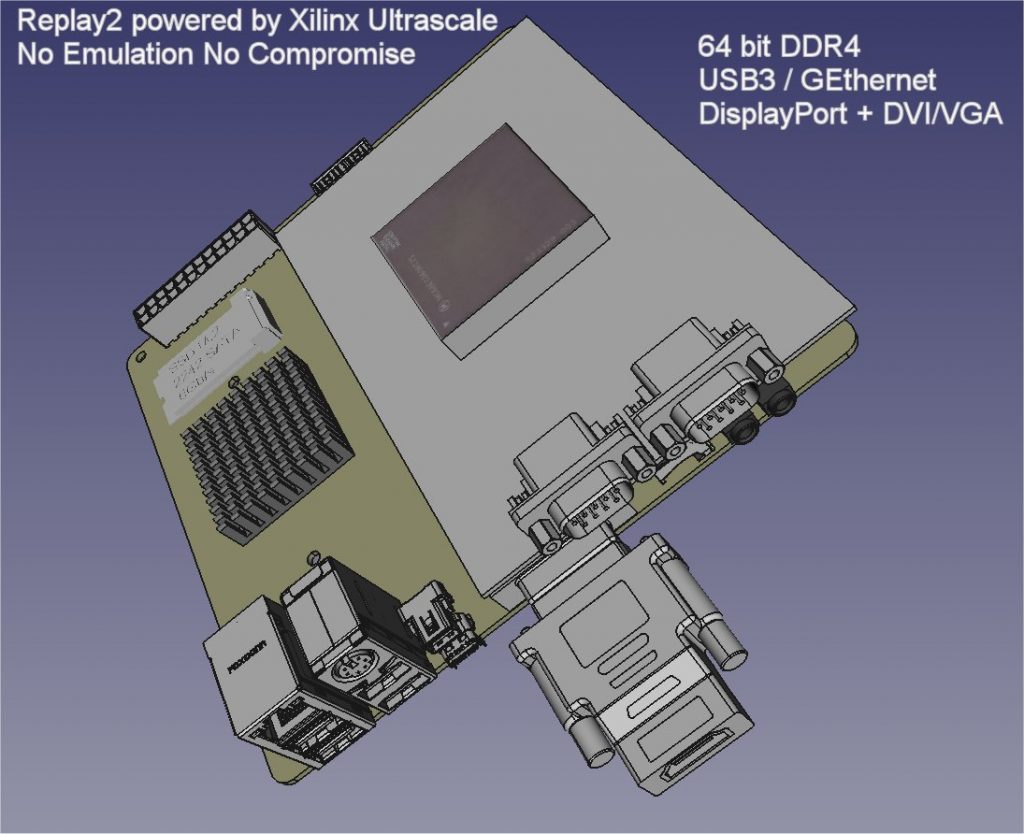

Replay2 is now in PCB design. We are using a Xilinx Ultrascale+ MPSoC device which combines a fast FPGA and a 64 bit Cortex A53 cluster. The device is built on 16nm FinFET+ logic. The processor system runs up to 1.5GHz, and will have 64bit DDR4 memory (which can be shared with the FPGA). There will be an additional memory directly attached to the FPGA to give low-latency storage to the core.

We also get USB3, Gigabit Ethernet, Display Port (primarily to debug the CPU software), PCI Express/SATA which we may use for M.2 storage. Finally, depending on the device and pricing we get from Xilinx, we may be able to use a device which contains a Mali GPU.

The board is a mini-ITX form factor to easily fit in cases. We also have an expansion option, for a 68060 processor or alternative console IO connectors for example.

/MikeJ

Replay2 …. the saga continues

So first, I must apologise for it being quiet here news-wise. The active development is mostly on Slack now, but I will try and post updates here more often.

So, Replay2 stalled. The issue was the excellent price/performance of the DE10 board (used in the Mister project) which is available for $130. While add on boards are needed, the total price is around $200 – and you get a very capable FPGA for this due to Intel’s education discounts.

The device used on the DE10 is a Cyclone® V SE 5CSEBA6 which has 160K flops and a dual 800MHz A9 processor.

Comparing this with the FPGA on the Vampire V4 5E 5CEFA5F23C for example, 116K flops and no CPU, you realize what a bargain the DE10 is.

I waited a long time for Xilinx to release a low end 7-series device to compete with Cyclone V, Spartan7, and it became available last year. The XC7S75-2 device I selected, 96K flops and no CPU, was reasonable – but I did need a CPU. I selected the Artik710 module, however as layout was nearing completion it was EOL (end of life’d). Boo.

So, I was talked into giving the Xilinx Zynq another look. The XC7Z7020-2 has a 766MHz dual processor, so close, but only 106K flops. We would need to go to the XC7Z7030-2 to be just competitive with the DE10, and the pricing isn’t there. Anyhow, it’s old – launched in 2011 – and when compared with say the RK3399 SOC (2x A72 @ 2GHz, 4 x A54@1.5GHz, Mali-T864) for $20, it’s extremely hard to look competitive.

The Spartan3E/6 devices are excellent value for money even now, but the toolchain has been frozen since 2013 – the newer tool only supports 7 series or later devices. This probably makes a lot of sense for Xilinx, but it means no system verilog support for my board, and it’s hard to get people to use a “dead” tool.

However, as the original developer of FPGA games …

A simulation model of Pacman hardware

Copyright (c) MikeJ – September 2002

we don’t give up easily. I’m in the process of designing Replay2 based on a Xilinx Ultrascale MPSoC device. This will offer a 64bit ARM A53 processor cluster, fast DDR4 memory and USB3. It’s certainly overkill for the simple games, but it will enable us to make the most amazing Amiga and Atari cores, as well as opening the door to “hybrid emulation” where we run some CPU emulation on the ARM cores, and the backend in the FPGA. More details to follow as we firm up the design.

Finally, the last few 68060 Daughterboards – if you have a Replay1 board and you want to have the fastest 060 based Amiga around, let me know. I have a few spare still.

/MikeJ

Replay2

Over the years there has been a lot of frustration about the lack of Replay boards. The main issue was the lack of quality control on components from China which caused a lot of rework effort. In retrospect, we should probably have thrown these away and built new ones….

I’ve been working with some contacts and have now learned enough to get them manufactured and shipped in volume. While the current Spartan3E based Replay board is quite capable of running anything we can throw at it, it’s getting harder to source components and the FPGA is not supported by the new Xilinx toolchain, so after a lot of discussion we’ve decided to move ahead and make Replay2.

Xilinx have been rather late producing the Spartan7 FPGA I’ve been waiting for, and other solutions such as the DE-10 SOC board are already shipping in volume at an amazing price. So why bother?

Well, I prefer to have a complete solution which has all the bits on we need, including decent quality analog outputs. I’ve used embedded Linux on FPGAs before, but I’ve gone for a lightweight solution here with a separate ARM. This is pretty cost effective and means the system is easier to get to grips with from both the software and core perspective. It also gives, in my view, a more uniform look and feel to the system across the cores.

The current replay board is still supported – all the board specific stuff is currently abstracted in the Replay support library, and this will be enhanced to support the additional PHYs and DRAM. We’ve kept the DDR1 memory as well so we can immediately run up the current cores (and focus on porting others)

It’s currently being prototyped and the design is in PCB layout. I hope we will see it towards the end of the year.

/MikeJ